Parallel Input Serial Output Shift Register Verilog Code

- Parallel Input Serial Output Shift Register Verilog Code Download

- Parallel Input Serial Output Shift Register Verilog Code List

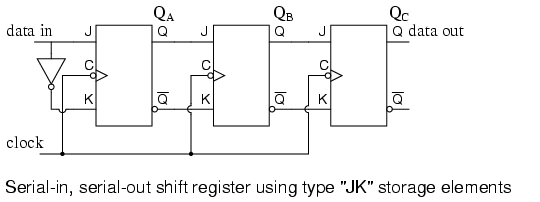

> can any 1 help me in writing a code for 6 to 16 bit programmable > parallel to serial converter. What do you have already done? Show your work and then ask your questions. > for 6 to 16 bit programmable parallel to serial converter. Is that a simple loadable shift register? Draw a picture or just add more information.

| Output Waveform : Parallel IN - Serial OUT Shift Register |

- Verilog - 13 Restricted FSM Implementation Style ˙ '!! ˙˝% )7 ˙˝% i% ˙ ˙˝ ˙ r ˙!

- 90 Responses to “Verilog HDL Program for Serail In – Serial Out Shift Register” Reva Pickrell May 23, 2018 AliExpress features items from sellers all all over the world.

VHDL Code-

-------------------------------------------------------------------------------

--

-- Title : parallel_in_serial_out

-- Design : vhdl_upload2

-- Author : Naresh Singh Dobal

-- Company : nsdobal@gmail.com

-- VHDL Programs & Exercise with Naresh Singh Dobal.

--

-------------------------------------------------------------------------------

--

-- File : Parallel IN - Serial OUT Shift Register.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity parallel_in_serial_out is

port(

clk : in STD_LOGIC;

reset : in STD_LOGIC;

load : in STD_LOGIC;

din : in STD_LOGIC_VECTOR(3 downto 0);

dout : out STD_LOGIC

);

);end parallel_in_serial_out;

architecture piso_arc of parallel_in_serial_out is

begin

piso : process (clk,reset,load,din) is

variable temp : std_logic_vector (din'range);

begin

if (reset='1') then

temp := (others=>'0');

elsif (load='1') then

temp := din ;

elsif (rising_edge (clk)) then

dout <= temp(3);

temp := temp(2 downto 0) & '0';

end if;

end process piso;

end piso_arc;

I am making a parallel to serial converter using ring counter in verilog. The ring counter is working fine but the Parallel to serial converter is not working properly and I am getting x undefined result. I am providing the code kindly help me finding the problem.

TOP

Parallel TO Serial Converter

RingCounter

1 Answer

I think the main issue you are seeing is part of parToser.

You have reg [2:0]i; which you increment and use to address input [3:0] myout; but i can hold values 0 to 7, half of which is outside the address range of [3:0] myout. You should be seeing a simulation error about out of range addressing.

Source code aplikasi penjualan barang kasir. Also you have included a few flip-flops with a reset condition but not added the reset to the sensitivity list in 'parToser' & 'Ring':

Crtani na hrvatskom. Should be:

Parallel Input Serial Output Shift Register Verilog Code Download

With out this trigger your out, i and myout variables will be x, as they have not been set to a known condition.

Parallel Input Serial Output Shift Register Verilog Code List

NB: parToser i = i+1; should be i <= i+1;